# A SOFTWARE ARCHITECTURE-BASED TESTING TECHNIQUE

By Zhenyi Jin A Dissertation Submitted to the Graduate Faculty of George Mason University In Partial Fulfillment of The Requirements for the Degree of Doctor of Philosophy Information Technology Committee: A. Jefferson Offutt, Dissertation Director \_\_\_\_\_ Chairman Paul Ammann \_\_\_\_\_ X. Sean Wang Elizabeth White Stephen G. Nash, Associate Dean for Graduate Studies and Research Lloyd J. Griffiths, Dean, School of Information Technology and Engineering Date: \_\_\_\_\_ Summer 2000 George Mason University Fairfax, Virginia

# A SOFTWARE ARCHITECTURE-BASED TESTING TECHNIQUE

A dissertation submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Information Technology at George Mason University

By

Zhenyi Jin Master of Computer Science George Mason University, 1994

Director: A. Jefferson Offutt, Associate Professor Department of Information and Software Engineering

> Summer Semester 2000 George Mason University Fairfax, Virginia

# COPYRIGHT 2000 ZHENYI JIN ALL RIGHTS RESERVED

# DEDICATION

This dissertation is lovingly dedicated to

# ACKNOWLEDGMENTS

I want to thank

# **Table of Contents**

| TABLE OF CONTENTSV                                    |                                                                         |     |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------|-----|--|--|--|

| CHAPTER 1INTRODUCTION                                 |                                                                         |     |  |  |  |

|                                                       | General Introduction                                                    |     |  |  |  |

|                                                       | Goals and Scope of This Research                                        |     |  |  |  |

|                                                       | Solution Strategy                                                       |     |  |  |  |

|                                                       |                                                                         |     |  |  |  |

| 1.4                                                   | Unique Contributions of the Research                                    | 9   |  |  |  |

| 1.5                                                   | Dissertation Organization                                               | 9   |  |  |  |

| CH                                                    | CHAPTER 2 BACKGROUND AND RELATED WORK                                   |     |  |  |  |

| 2.1                                                   | Background                                                              |     |  |  |  |

| 2.2                                                   | Petri Nets                                                              | 21  |  |  |  |

| 2.3                                                   | Software Testing                                                        |     |  |  |  |

| 2.4                                                   | Issues in Software Architecture-Based Testing                           |     |  |  |  |

| 2.5                                                   | General Properties to Be Analyzed and Tested at the Architectural Level |     |  |  |  |

| 2.6                                                   |                                                                         |     |  |  |  |

|                                                       |                                                                         |     |  |  |  |

| CH                                                    | APTER 3A SOFTWARE ARCHITECTURE-BASED TESTING TECHNIQUE                  | 35  |  |  |  |

| 3.1                                                   | Basic Definitions                                                       |     |  |  |  |

| 3.2                                                   | Architecture-based Testing Technique for General ADLs                   |     |  |  |  |

| 3.3                                                   | Architecture-based Testing Criteria                                     | 57  |  |  |  |

| 3.4                                                   | Architecture Coverage Analysis                                          | 59  |  |  |  |

|                                                       |                                                                         |     |  |  |  |

| CH                                                    | APTER 4 TESTING TECHNIQUE APPLIED TO WRIGHT                             | 62  |  |  |  |

| 4.1                                                   | ADL Wright in Brief                                                     |     |  |  |  |

| 4.2                                                   | Mapping Wright to Interface Connectivity Graphs (ICG)                   |     |  |  |  |

| 4.3                                                   | Mapping Wright to Behavior Graph (BG)                                   |     |  |  |  |

| 4.4                                                   | ICG and BG Relations                                                    | 95  |  |  |  |

| 4.5                                                   | Generating Test Requirements and Test Cases                             | 97  |  |  |  |

|                                                       | Discussion                                                              | 105 |  |  |  |

| <b>-</b> .0                                           | D15Cu551011                                                             | 105 |  |  |  |

| CH                                                    | APTER 5 PROTOTYPE TOOL                                                  |     |  |  |  |

| 5.1                                                   | System Description                                                      | 106 |  |  |  |

|                                                       | Assumptions and Design Structure                                        |     |  |  |  |

|                                                       | 1 0                                                                     |     |  |  |  |

| CHAPTER 6 VALIDATION METHOD AND AN APPLIATION EXAMPLE |                                                                         |     |  |  |  |

| 6.1                                                   | Experiment Design                                                       | 125 |  |  |  |

| 6.2                                                   | Experimental Results                                                    | 135 |  |  |  |

| 6.3                                                   | Conclusion                                                              | 138 |  |  |  |

| CHAPTER 7 CONTRIBUTIONS AND FUTURE RESEARCH              |     |

|----------------------------------------------------------|-----|

|                                                          |     |

| APPENDIX A WRIGHT LANGUAGE IN BNF                        |     |

| APPENDIX B WRIGHT PROCESSES AND EVENTS                   | 147 |

| APPENDIX C SUBJECT PROGRAM WRIGHT DESCRIPTIONS AND TESTS |     |

| APPENDIX D BEHAVIOR GRAPHS OF THE SUBJECT SYSTEM         |     |

|                                                          |     |

| REFERENCES                                               |     |

# List of Figures

| 8   |

|-----|

| .22 |

| .24 |

| .24 |

| .25 |

| .36 |

| .38 |

| .43 |

| .52 |

| .53 |

| .53 |

| .54 |

| .55 |

| .55 |

| .56 |

| .56 |

| .57 |

| .59 |

| .62 |

| .68 |

| .69 |

| .72 |

| .76 |

| .78 |

| .79 |

| .80 |

| .82 |

| .83 |

| .84 |

| .85 |

| .86 |

| .87 |

| .88 |

| .89 |

| .90 |

| .91 |

| .91 |

| .93 |

|     |

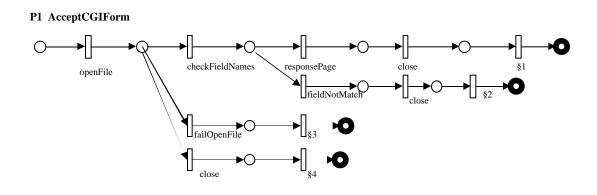

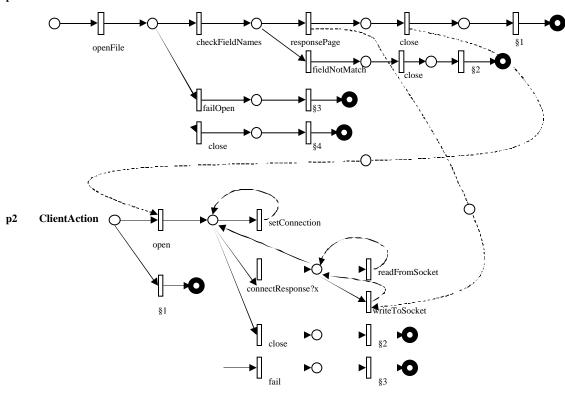

| Figure 4-21 | A Wright to BG Example            | 95   |

|-------------|-----------------------------------|------|

| Figure 4-22 | ICG and BG Relation               | 96   |

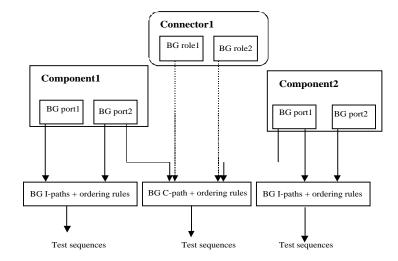

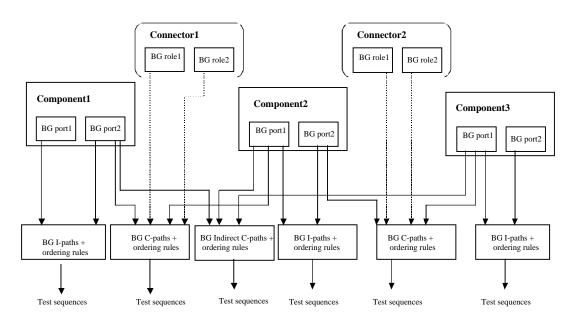

| Figure 4-23 | Test Set Generation 1             | .101 |

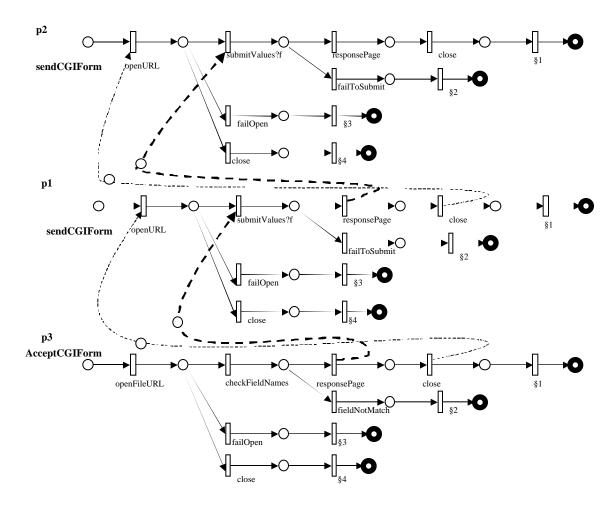

| Figure 4-24 | Test Case Generation 2            | .101 |

| Figure 4-25 | Test Case Generation 3            | .102 |

| Figure 4-26 | Test Case Generation 4            | .102 |

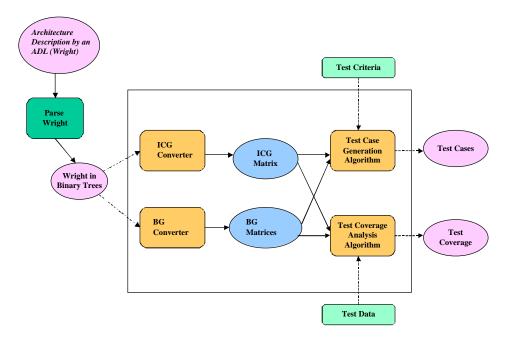

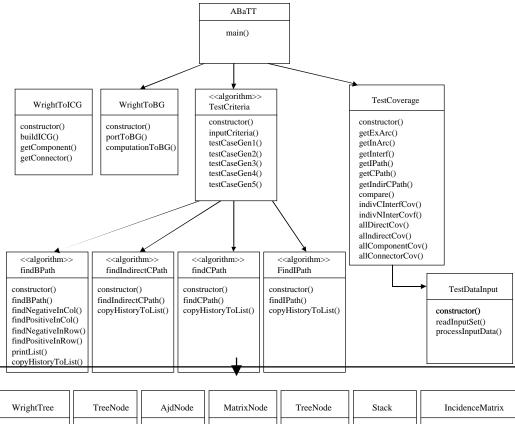

| Figure 5-1  | The Prototype Tool ABaTT          | .107 |

| Figure 5-2  | Wright in the Form of Binary Tree | .108 |

| Figure 5-3  | The ABT Class Structures          | .110 |

| Figure 5-4  | Algorithm buildICG                | .111 |

| Figure 5-5  | Algorithm wrightToBG              | .113 |

| Figure 5-6  | Algorithm combineTwoNets          | .115 |

| Figure 5-7  | Algorithm expandMatrix            | .116 |

| Figure 5-8  | Algorithm findBPath               | .118 |

| Figure 5-9  | Algorithm findCPath               | .119 |

| Figure 5-10 | Algorithm findIPath               | .120 |

| Figure 5-11 | Algorithm findIndirecCPath        | .121 |

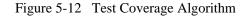

| Figure 5-12 | Test Coverage Algorithm           | .123 |

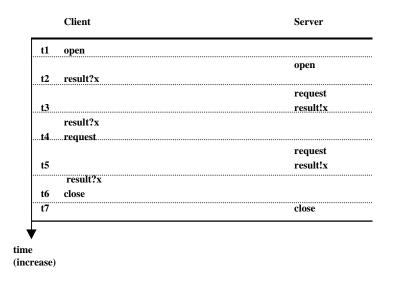

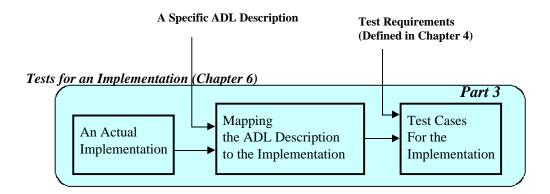

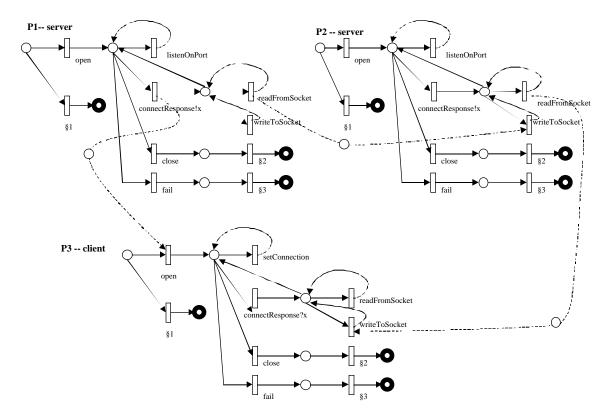

| Figure 6-1  | Tests For an Implementation       | .124 |

|             | Experiment Procedure              |      |

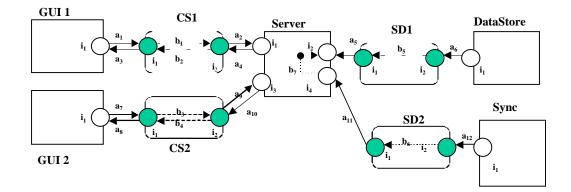

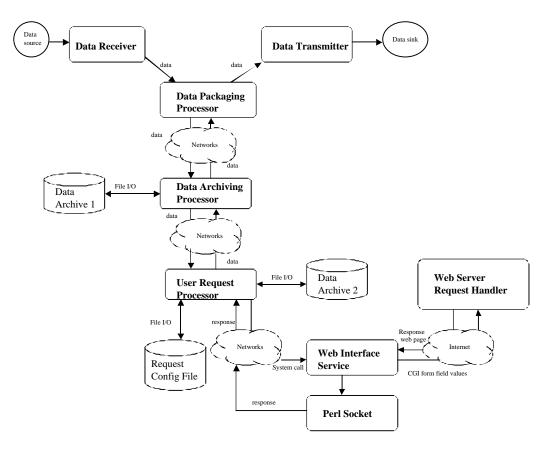

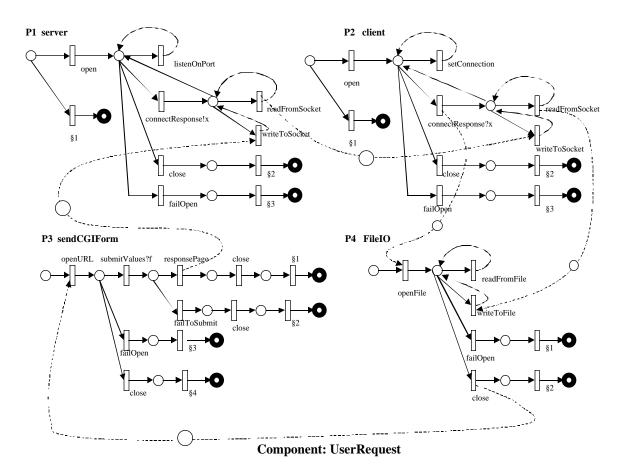

| Figure 6-3  | The Subject Program               | .130 |

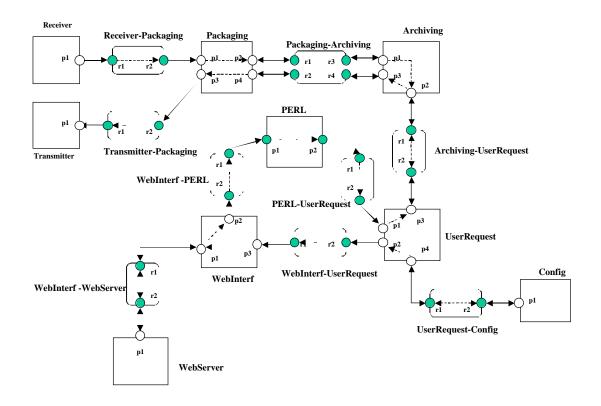

| Figure 6-4  | The ICG of the Subject Program    | .135 |

#### ABSTRACT

### A SOFTWARE ARCHITECTURE-BASED TESTING TECHNIQUE

Zhenyi Jin, Ph.D.

George Mason University, Fall 2000

Dissertation Director: Dr. A. Jefferson Offutt

This dissertation defines a formal technique to test software systems at the architectural level, particularly for software systems developed using software Architecture Description Languages (ADL). There is a lack of formally defined testing techniques at the architecture level. Formalized software architecture description languages provide a significant opportunity for testing because they precisely describe how the software should behave in high level view, and they can be used by automated tools. The basic theme in this dissertation is that many system architectural problems can be addressed through architecture relations, which are the paths through which architectural components communicate with each other. This dissertation presents a practical, effective, and automatable technique for testing architecture relations at the architecture level. This dissertation also presents a proof-of-concept tool to generate test requirements. An empirical evaluation is carried out to measure the fault finding effectiveness of the architecture-based testing criteria. Results show that this technique is effective at finding faults at the architecture level.

# **Chapter 1** Introduction

### **1.1 General Introduction**

The growing emphasis on modularity, data abstraction, and object-orientation in software design means that software systems are designed by using abstraction as a way to master complexity. As the size and complexity of software systems increase, problems stemming from the design and specification of overall system structure become more significant issues than problems stemming from the choice of algorithms and data structures of computation [SG96]. The result is that the way groups of components are arranged, connected, and structured is crucial to the success of software projects. One of the benefits of this kind of design is that software components can be analyzed and tested independently, low level details can be hidden, which permits concentration to be focused on analysis and decisions that are most crucial to the stem structure. At the same time, this independence of components means that significant issues cannot be addressed until full system testing. Problems in the interactions can affect the overall system development and the cost and consequences could be severe. For example, AT&T Bell Lab's formal review of architectures in development organizations suggests that this is a major problem: "More than 50% of the trouble reports in some systems are related to communications interfaces within them." [ATT93]. Thus, system-level faults must be specifically tested for.

This dissertation describes research to develop a new software testing technique at the system level. The technique is based on software architectures, which specify the primary

components, interfaces, connections and configurations of software systems. Although formal unit and module testing criteria have been well studied, system testing is typically done informally, using manual, ad-hoc techniques [You96]. This informality makes it difficult to measure the quality of testing, leads to a lack of repeatability in the process and results, and it means that the tester cannot be confident in the efficacy of the testing. Unit testing metrics are often used to measure the quality of system testing [Bei90]. For example, system tests are often evaluated by measuring how many statements are executed in the code. This kind of approach is clearly used only because there is no better metric; the two abstractions (system-level and statement-level) are so divergent that there is almost no possibility that a measurement designed for one level can be meaningful at the other. Unit testing techniques have also sometimes been used to directly generate tests for system-level testing, but there are two problems with this approach. First, this process is simply too expensive to be practical, and second, the kinds of faults that occur at the system level are different from those found during unit testing, and there is no reason to believe that unit testing techniques will find these kinds of faults. Those software faults cannot be detected during unit, module, or integration testing are often faults in the way the software components are structured or in how they communicate. Correctly implementing interactions can be difficult because unlike the components of a software system, the interactions are rarely isolated in a single, independent runtime structure. In stead, interaction is typically spread across the components involved in the interaction. To make matters more difficult, this interaction code is often tightly integrated with the code associated with the component's functionality.

The central problem of test data generation is that the only way to ensure complete correctness is to test with all possible inputs. Unfortunately, the number of possible inputs to a

given program is effectively infinite, to testers must accept partial results by finding a finite number of test cases that will provide a high level of confidence that the program is correct.

When performing system testing, testers are concerned with aspects of communication among the software components and subsystems, whether the structure of the software system can satisfy all the requirements, and whether the overall software system solve the problem. Software architecture design and specifications is at a level of abstraction above the traditional design process. Software architecture serves as a framework for understanding system components and their interrelationships, especially those attributes that are consistent across time and implementations. This understanding is necessary for the analysis of existing systems and the synthesis of future systems. For this reason, software architecture has drawn intensive attention from both academics and industry. At the software architecture level, software systems are presented at a high level of abstraction where a software system is viewed as a set of compositional components, interactions among these components, and the configuration of the system. Implementation details are suppressed and the independence of system components is increased, which permits concentration to be localized at analysis and decisions that are most crucial to the system structure. One idea that differentiates the study of software architecture from earlier work in module interconnection [Pur94] is that interaction between components must be made explicit and must be formalized. This means that software architectures, particularly when defined formally using some sort of architectural description language, can provide a description of the software system that could be used for tests generation at the system level. This enables developers to abstract away the unnecessary details and focus on the big picture of the system: system structure, high-level communication protocols, the assignment of software components and connectors to hardware components, development process, and so forth. The basic goal of software architecture research is to create better software systems by modeling their important aspects throughout and especially early in the development. Another promising potential of software architecture is to the reuse of software components and connections.

One continuing trend in software engineering is towards more formalized descriptions of software artifacts. Software architecture research is continuing this trend by introducing architecture description languages (ADLs) that capture the system level details of components, interactions and configurations. One important contribution of these languages is the fact that interaction is first class. In an ADL, the interaction between components is defined explicitly. In some ADLs, connector types can be defined as well and these can be instantiated and used to describe interactions between objects of some given component types [MQ94].

Formalized software architecture design languages provide a significant opportunity for testing because they precisely describe how the software is supposed to behave in (1) a high level view that allows test engineers to focus on the overall system structure, (2) a form that can be easily manipulated by automated means. Finding ways to use ADLs to drive the process of analyzing and testing software systems is an important new avenue of research.

Evaluating and testing software systems at the architecture level can allow tests to be created earlier in the development process, therefore substantially reducing the costs of any problems and errors. Currently, there is a lack of testing techniques for testing at the software architecture level. In this dissertation, we present a research in the area of software architecturebased testing to create a general testing technique at this level.

## 1.2 Goals and Scope of This Research

Software architecture-based testing is crucial to the overall quality of software systems. Architecture level errors may severely impact the software in ways that are costly to fix and that cause catastrophic consequences in safety critical systems. Currently, there is a lack of formal testing methods for testing at the software architecture level. The few research techniques that exist are either limited in scope or use traditional implementation-based (programming language dependent) testing methods to test at the software architecture level. Also, there are no generalpurpose tools to actually generate tests for testing at the software architecture level.

#### **1.2.1** Problem statement

There are no general methods for software architecture-based testing. This thesis seeks to address the problem of defining test criteria and generating test cases for testing at the software architecture level.

### 1.2.2 Thesis Statement

This thesis seeks to solve the problem by formally defining testing criteria for software architectures and automating test case generation based on these criteria in a well known architecture definition language (ADL), Wright.

#### **1.2.3** Scope of Research

This dissertation investigates the following research problems:

1. Develop testing criteria for generating software architecture level tests from software architecture descriptions.

These criteria can be used both to guide the architecture designers and to help the testers generate meaningful and effective test cases.

Define test requirements to be derived from testing criteria on one or more specific ADLs.

These test requirements are generated directly from the criteria, and they describe specific inputs to the software at the system level.

3. Develop algorithms to automatically create test requirements, then to automatically generate test inputs.

These algorithms are based on a specific ADL description. When the selection of an ADL changes, the algorithm remains the same at the top level, but may vary depending on specific ADL features as lower level descriptions are reached.

4. Develop a proof-of-concept tool to generate test cases automatically from a Wright specification.

This tool generates incidence matrices (to represent two types of graphical representations) of architectures and uses these formalisms to generate appropriate test cases to satisfy the testing criteria.

5. Empirical validation.

The architecture-based testing technique is applied to an industrial software system. The results are compared with results from using other two testing methods. The goal of this process is to determine whether the new testing technique can effectively detect faults.

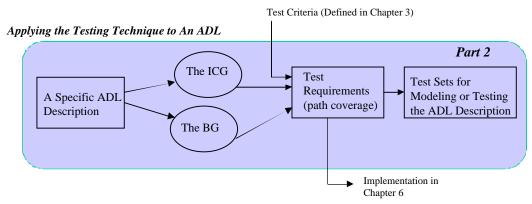

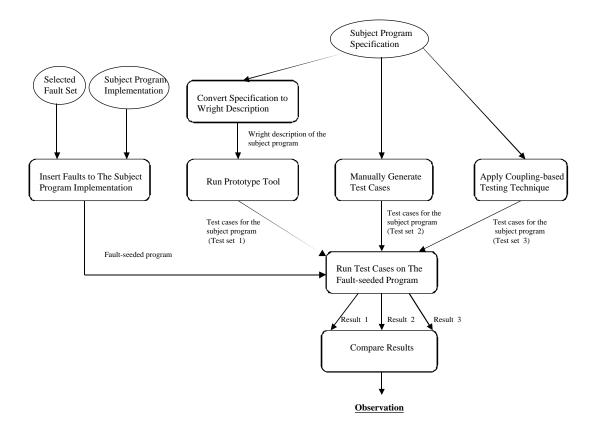

## **1.3** Solution Strategy

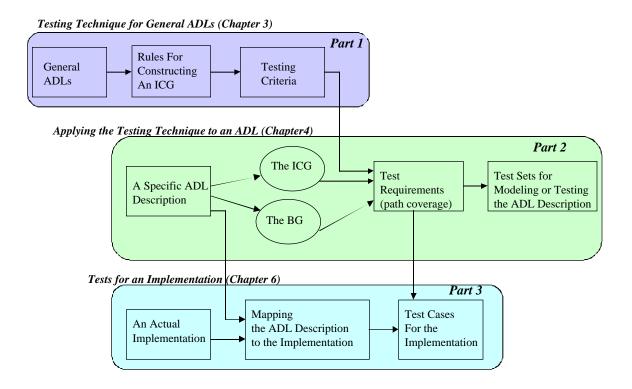

In order to find solutions to our research problems, first we discuss issues of testing at the architecture level, then list a set of properties that should be tested for at the software architecture level. This helps us to decide what to test when testing at the architecture level. Then we define architecture relations at the architectural level, and formally define these relations. Two graphical representations are introduced for testers to visualize the testing technique and for possible analysis and simulations. Testing criteria are then discussed based on the architecture relations. These criteria are classified and formally defined. Further, test requirements can be derived from these testing criteria and the graphical representations. We then apply the technique to a specific ADL, Wright, and develop algorithms to transform the Wright specification to two graphical representations. An empirical evaluation of the technique is carried out using an industrial software system, its evaluation results are discussed. The overall solution topology is shown in Figure 1-1, where there are altogether three parts, *Testing technique for general ADLs, Applying the technique to an ADL*, and *Tests for an implementation*. Each of these three parts will be discussed in further detail in the next few chapters.

Figure 1-1 The Solution Topology

### **1.3.1** A Brief Description of The Research Results

A general software architecture-based testing technique is defined in this dissertation. Testing criteria are formally classified and defined. Test requirements can be derived for a specific ADL description. Evaluation results show that when applying this technique to the ADL Wright, test cases can be generated automatically, and these test cases can find more faults at the architecture level than manual method or coupling-based testing technique. Test coverage can be determined given some test case sets.

## **1.4 Unique Contributions of the Research**

Major contributions of this dissertation are listed as follows:

- 1. Formal definitions of criteria for testing software architcture-based software systems

- 2. Formal definition of a general-purpose technique for testing software architecture

- 3. Formal definitions of architecture relations

- 4. Petri net based architecture modeling technique

- Formal definitions of transformation rules for translating Wright specification to revised Petri Nets

- 6. Prototype tool for generating test case based on Wright descriptions

## 1.5 Dissertation Organization

Chapter 2 reviews background and related research. Chapter 3 discusses the architecturebased testing technique for general ADLs. An application of the technique to the ADL Wright is presented in Chapter 4. Chapter 5 presents a proof-of-concept-tool and an empirical validation of the technique is discussed in Chapter 6. Finally, Chapter 7 concludes the dissertation research and discusses future research directions.

# Chapter 2 Background and Related Work

This chapter gives background information in software architecture, summarizes related software testing techniques, discusses issues in architecture-based testing, presents the basics of a specific architecture description language Wright, and overviews Petri nets, which will be used as an intermediate form of representation for our testing and possible analysis.

#### 2.1 Background

This section discusses some background information this dissertation work is based on. General information about software architecture, software architecture description languages, Petri Net basics, and software testing technique are presented in this section.

#### 2.1.1 Software Architecture

The study of software architecture has evolved from the seminal work of Perry and Wolf [PW92], Garlan and Shaw [GS93], and others to the classification of architectural styles, architecture evaluation [KBA+94], formalized representation, and application of domain specific architectures (DSSAs) [DSSA92]. The term "software architecture" is often used in software engineering. One of the reasons is that "architecture" indicates an association with the construction of actual buildings. Software engineers try to find an analogy between the architecture design and development of buildings and that of software. In general, two groups are considered to have laid the conceptual basis for software architecture. Perry and Wolf

[PW92] describe an overall software architecture as a mediator between requirements and design. They view software architecture as elements + form + rationale, where the elements are divided into three classes: processing elements, data elements, and connecting elements. Since data elements and processing elements have been studied intensively in the past as functions or objects, it is the connecting elements that especially distinguish one architecture (or style) from another. Rationale describes quality attribute aspects [Abd-Allah96]. An architecture style is viewed as constraints on a class of architecture; there is no clear distinction between instances and styles. An architecture configuration consists of a collection of constraints. Shaw and Garlan [GS93, SG94, SG95] describe software architecture as a necessary step in raising the level of abstraction at which software is conceived and developed. They view software architecture as components + connectors; a family of architectures + constraints defines an architectural style. A model of architecture is a set of components together with a description of the interactions (connectors) between these components. Architectural styles are a family of systems (architectures) that share repeating patterns of computation and interaction, together with rules for how these are used in specific configurations. Garlan and Shaw presented a partial taxonomy of known architecture styles [SG96]. They listed twelve styles as Layered, Distributed processes and threads, Pipes and filters, Object-oriented, Main program/subroutines, Repositories, Event-based (Implicit invocation), Rule-based, State transition based, Process control (feedback), Domain-specific and Heterogeneous. Quality attributes are not described from Garlan and Shaw's view of software architecture. Also, the rationale defined by Perry and Wolf is not present.

The ARPA Domain Specific Software Architecture (DSSA) program [Ves93] defines software architecture as an abstract system specification consisting primarily of functional components described in terms of their behaviors and interfaces and component-component interconnections. Architectures are usually associated with a rationale that documents and justifies constraints on component and interconnections or explains assumptions about the technologies that will be available for implementing applications that are consistent with the architecture [HAYE94]. An architecture is viewed as Components + Styles + Common patterns of interaction between functional components.

The software architecture group of USC [GACB95] expands the notion of software architectures into "system software architectures" with a set of criteria for identifying them. They define a set of stakeholders (Customer, User, Architect and System Engineer, Developer, Maintainer) and make the architectural rationale to ensure that the architecture's components, connectors and constraints will satisfy the stake holder's needs. An architecture should be composed of alternate views including a behavioral/operational view, a static topological view, and a data flow view. Their formal architectural notations should be able to capture all these views together with other views that are concerned with other stakeholder needs.

Although true consensus may be hard to achieve or not necessary, it is generally accepted that software architectures identify the following software attributes. We use general definitions described in Moriconi and Qian's paper [MQ94]:

- Component: An object with independent existence, e.g., a module, process, procedure, or variable.

- *Interface:* A typed object that is a logical point of interaction between a component and its environment.

- *Connector:* A typed object relating interface points, components, or both.

Configuration: A collection of constraints that wire objects into a specific architecture.

*Architectural style*: A style consists of a vocabulary of design elements, a set of well-formed constraints that must be satisfied by any architecture written in the style, and a semantic interpretation of the connectors.

Components, interfaces, and connectors are used as first-class objects, i.e., they each has a name and they can be refined (can be decomposed into a set of components, connectors, and interfaces). Abstract architectural objects can be decomposed, aggregated, or eliminated in a concrete architecture.

For instance, in a distributed system architecture, subsystems are components, and network protocols are connectors. Components participate in the component interactions to initiate communication, generate messages, and respond to other components' requests. The interfaces of the connectors and components have to be consistent to keep the interactions active. The organization of these components and connectors form the configuration of the architecture. For instance, the ring or star architecture topology forms different configurations of the system.

#### 2.1.2 Architecture Description Languages

Architecture Description Languages (ADL) have been proposed as modeling and design notations to support analysis and development of architecture-based development. Most of them use formal approaches for architecture representations. ADLs have recently been an area of intense research in the software architecture community [Gar95, Wolf96].

A number of ADLs have been proposed for modeling architectures both within a particular domain and as general-purpose architecture modeling languages. Here we introduce nine ADLs.

1) Rapide: developed by Luckham, et al. [LV95, LKA+95] of Stanford University for the DARPA Prototech program, Rapide is designed to support component-based development of large, multi-language systems by using architecture definitions as the development framework. Rapide adopts a event-based execution model of distributed, time-sensitive systems -- the "timed partial ordered set (poset) model." Posets provide the most detailed formal basis to date for constructing early life cycle prototyping tools, and later life cycle tools for correctness and performance analysis of distributed time-sensitive systems. Rapide supports simulation of systems in general before they are implemented. It is event-based and object-oriented. Rapide architectures of systems are described in terms of the events that occur and are passed between system entities; posets are used to describe system behavior. There are actually five independent sub-languages within Rapide: (1) type language to describe the interfaces of components, (2) architecture language to describe the flow of events between components, (3) specification language to write abstract specifications of component behavior, (4) executable language to write executable bodies for components, and (5) pattern language to describe patterns of events [LV95, LKA+95]. Automated analysis for behavior or timing problems such as deadlock or improper event orders has been done. Rapide does not explicitly support software architecture styles, and has in fact a bias towards event-based systems.

2) **Aesop:** developed by the ABLE project at Carnegie Mellon University [Gao94]. Aesop creates a software architecture design environment that is specialized to support design in the styles that it has taken as input. It provides a general framework for defining many architectural languages, each specialized to a particular architectural style. The core of Aesop is a generic architectural description language called ACME, from which the other more specialized forms are developed.

3) **UniCon** (language for UNIversal CONnector support) : developed by Shaw of Carnegie-Mellon [SDK+95], UniCon emphasizes the structural aspects of software architecture and is based on the complementary constructs of component and connector.

4) **MetaH:** developed by Vestal, et al. [Ves96] of Honeywell for the DSSA project, MetaH is intended to support analysis, verification, and production of real-time, fault-tolerant, secure, multi- processing, embedded software.

5) LILEANNA (Library Interconnect Language Extended with ANNotated Ada): developed by the Loral (now Lockheed Martin) DSSA team and Don Batory [Tra93] to support abstraction, composition, and reuse of Ada software. LILEANNA has been applied to avionics domain and is composed of LIL — a module composition language for Ada — and ANNA — a language that facilitates automated analysis of formal specifications and composition of Ada code.

6) **C2**: developed by a research group at UC Irvine [MTW96, MORT96, Med96]. C2 is UCI's component- and message-based architectural style for constructing flexible and extensible software systems. A C2 architecture is a hierarchical network of concurrent components linked together by connectors (or message routing devices) in accordance with a set of style rules. C2 communication rules require that all communication between C2 components be achieved via message passing.

7) **Darwin**: describes a component type by an interface consisting of a collection of services that are either provided or required. Configurations are developed by component instantiation declarations and binding between required and provided services [MDEK95, MK96]. It supports the description of dynamically reconfiguring architectures through two

constructs – lazy instantiation and explicit dynamic constructions. Darwin provides a semantics for its structural aspects through the -calculus [MPW92].

8) **ACME**: proposed as an architecture interchange language [GMW95, GMW97] to support unifying existing ADLs, and hence provide a bridge for their different focuses and resulting supporting tools. ACME uses components, connectors and configurations to model the composition of a system.

9) **Wright**: is an architectural specification language [AG94a, AG94b, All97] that makes the notion of first class connection precise by defining the semantics of connectors as formal protocols in a variant of CSP [Hoa85]. Because we are applying the architecture-based testing technique to Wright, details of Wright are introduced here.

#### 2.1.3 The ADL Wright

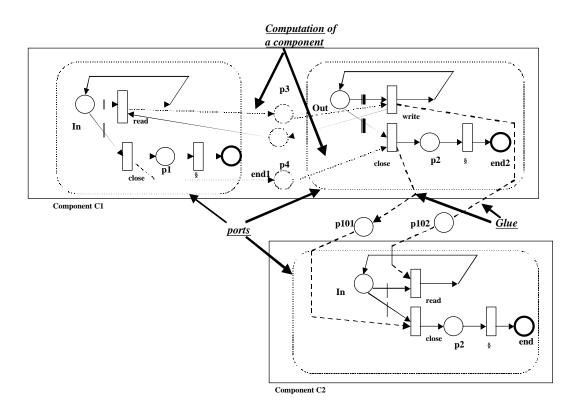

Wright is built on three basic architectural abstractions: *components, connectors, and configurations* [All97]. The description of a component has two parts: the *interface* and the *computation*. An interface consists of a number of *ports*. Each *port* represents an interaction in which the component may participate. A port specification indicates some aspect of a component's behavior as well as the expectations of a component about the system with which it interacts.

The *computation* describes what the component actually does. It carries out the interactions described by the ports and shows how they are tied together to form a coherent whole. Ports provide an additional level of abstraction, not to be redundant with the computation.

A Wright *connector* contains a set of *roles* and the *glue*. Each *role* specifies the behavior of a single participant in the interaction. The role indicates what is expected of any component that will participate in the interaction. The *glue* of a connector describes how the participants work together to create an interaction. Like the computation of a component, the glue of the connector represents the full behavioral specification. Glue processes coordinate the components' behavior to create an interaction. So a connector specification means that if the actual components obey the behaviors indicated by the roles, then the different computations of the components will be combined as indicated by the glue.

The components and connectors of a Wright description are combined into a *configuration* to describe the complete system architecture. To distinguish the different instances of each component and connector type that appear in a configuration, Wright requires that each *instance* be explicitly and uniquely named.

*Attachments* define the topology of the configuration by showing which components participate in which interactions. It associates a component's port with a connector's role.

In general, the component carries out a computation, part of which is a particular interaction, specified by a port. That port is attached to a role, which indicates what rules the port must follow in order to be a legal participant in the interaction specified by the connector. If each of the components, as represented by their respective ports, obeys the rules imposed by the roles, then the connector glue defines how the computations are combined to form a single, larger computation. A Wright structure example looks like this:

Component C1 Port [port description] Computation [computation description] Component C2

```

Port [port description]

Computation [computation description]

Connector C1-C2 Connector

Role [role description]

Role [role description]

Glue [glue description]

Instances

component1: C1

component2: C2

connect: C1-C2 Connector

Attachments:

component1 provides as C1-C2.C1

component provides as C1-C2.C2

end

```

A Wright Structure Example

Wright supports hierarchical descriptions. In particular the computation of a component or the glue of a connector can be represented either directly by a behavior specification or by an architectural description itself.

The behavior and coordination of components is specified using a notation based on CSP [Hoa85, All97]. CSP is a notation for specifying patterns of behavior and interaction. Here are some of the representations in Wright:

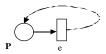

**Processes and Events**: The basic unit of a CSP behavior specification is an *event*. A *process* describes an entity that can engage in communication events. In Wright, observing an event and initiating an event is differentiated. An event that is initiated by a process is written with an overbar (underscore in this document because of software limitation) within that process' definition. A special event in Wright is §, which indicates the successful termination of the entire system. This event is not considered either to be initiated or observed. If a process supplies data, it is considered output, and is written with an exclamation point: **write!x**. If a process received data, it is input, and written with a question mark: **e?x**.

**Prefixing**: Given a process **P** and an event **e**, the process  $e \rightarrow P$  is the process that first engages in the event e and then behaviors as **P**.

Alternative ("external choice"): A process that can behave like **P** or **Q**, where the choice is made by the environment, is denoted by the operator  $\Box$ . The process  $\mathbf{e} \rightarrow \mathbf{P} \Box \mathbf{f} \rightarrow \mathbf{Q}$  is the process that will behave as the process **P** if it first observes the event **e** and will behave as the process **Q** if it first observes the event **f**. Because the behavior of the process is entirely determined by what the environment does, this type of choice is called deterministic. "Environment" refers to the other processes that interact with the process.

**Decision** ("internal choice"): A process that can behave like **P** or **Q**, where the choice is made (non-deterministically) by the process itself, is denoted **P**  $\Pi$  **Q**. The process  $\mathbf{e} \rightarrow \mathbf{P} \Pi \mathbf{F} \rightarrow \mathbf{Q}$  is the process that will either output  $\mathbf{e}$  and then act as **P** or output **f** and then act as **Q**. The process itself decides which choice to take without consulting the environment.

Sequence: The ";" operator combines two processes in sequence. P;Q is the process that behaves as P until P terminates successfully and then behaves as Q.

Behavior patterns that occur over and over again can be described by naming particular processes.  $P = e \rightarrow P$ . Named processes can also be introduced into other processes using Where:  $f \rightarrow P$  where  $P = e \rightarrow P$ . This process does a single **f** and then repeats **e** over and over.

State is added to a process definition by adding subscripts to the name of a process: **Pi** is a process with a single state variable, **i**. For example, **P1** where  $\mathbf{Pi} = \underline{\mathbf{count!i}} \rightarrow \mathbf{Pi+1}$  is a process that counts : **count!1, count!2, count!3**, etc. For more than state variables, simply add corresponding number of subscripts to the name of the process.

Pv = Q, when p(V) defines a process P over variables V only when the boolean expression

**p**(**V**) is true.

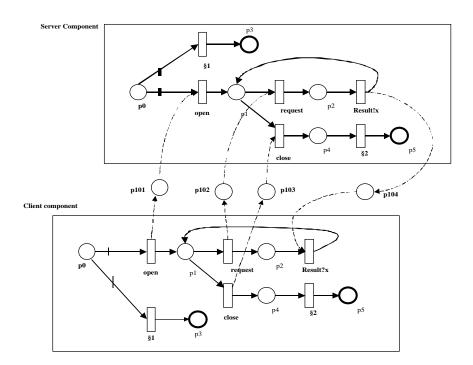

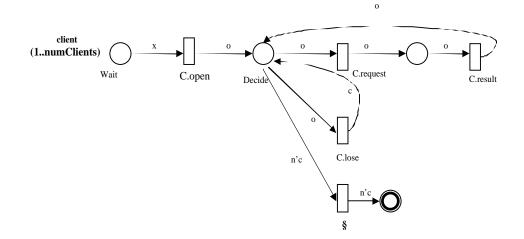

An example of the Client-Server architecture description is given as follows:

```

Component Client

Port Service = ClienPullT

Computation = Service.open ; UseOrExit

where UseOrExit = UserService \prod Exit

UseService = Service.request \rightarrow Service.result?y \rightarrow UseOrExit

Exit = Service.close \rightarrow §

Component Server

Port Provide= ServerPushT

Computation = WaitForClient □ Exit §

where WaitForClient = Provide.open \rightarrow Provide.request \rightarrow Provide.result?y

→ WaitForClient

Exit = Provide.close \rightarrow §

Connector C-S Connector

Role Client = ClientPullT

Role Server = ServerPushT

Glue = Client.open \rightarrow \underline{Server.open} \rightarrow Glue

\Box \text{ Client.close} \rightarrow \underline{\text{Server.close}} \rightarrow \text{Glue}

\Box Client.request \rightarrow Server.request \rightarrow Glue

\Box \text{ Server.result?x } \rightarrow \underline{\text{Client.result!x}} \rightarrow \text{Glue}

Instances

c: Client

s: Server

cs: C-S Connector

Attachments:

c provides as cs.c

s provides as cs.S

end

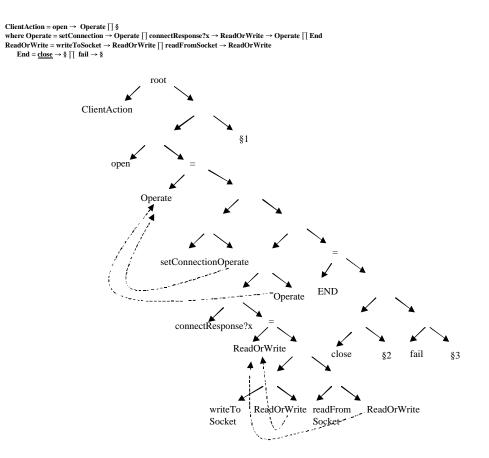

Interface Type ClientPullT = open \rightarrow Operate \prod §

where Operate = \underline{request} \rightarrow result?x \rightarrow Operate \prod Close

Close = \underline{close} \rightarrow \S

Interface Type ServerPushT = open \rightarrow Operate \square §

where Operate = request \rightarrow <u>result!x</u> \rightarrow Operate \square Close

Close = \underline{close} \rightarrow \S

```

Example: A Client-Server System in Wright

In CSP and also in Wright, the use of the term "process" does not mean that the implementation of the protocol would actually be carried out by a separate operating system process. Processes are logical entities used as specification building blocks. Also event is not an ordinary event, but has special rules associated with. See [ROS98] for details.

## 2.2 Petri Nets

Petri Nets have been introduced for modeling distributed systems because they give a graph-theoretic representation of the communication and control patterns, and a mathematical framework for analysis and validation [Peterson81, RT86, Jin94]. Petri Net modeling is appealing for the following reasons:

- Petri Nets capture the precedence relations and structural interactions of concurrent and asynchronous events. Petri Nets provide an integrated methodology, with welldeveloped theoretical and analytical foundations for modeling complex systems.

- The graphical nature of Petri Nets helps to easily visualize the complexity of the system.

- The mathematical representations of Petri Nets allow for quantitative analysis of invariants, deadlock detection, resource utilization, throughput rate, effect of failures, and real-time implementation.

- Petri Nets can be executed and can actually show the dynamics of the system. This makes the Petri Nets a powerful modeling language.

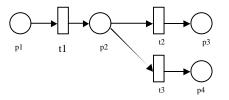

A Petri Net is a bipartite directed graph: N= (P, T, I, O). There are two sets of nodes:

- P = {p1, ..., pn} is a finite set of *places*. Each place pi models a resource, a buffer, or a condition. A place is depicted by a circle node.

- T = {t1, ..., tm} is a finite set of *transitions*. Each transition ti stands for a process, an event, or an algorithm. A transition is represented by a bar node.

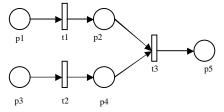

- The *arcs* that connect these nodes are directed and fixed. They can only connect a place to a transition, or a transition to a place. They are given by: I : P × T -> {0,1}, O : P × T -> {0,1}. I is an input function that defines the set of directed arcs from P to T. I(p,t) = 1 if the arc exists, I(p,t) = 0 otherwise. An arc from a place p to a transition t indicates that the process t requires the availability of the resource p, the fulfillment of the condition p, or the availability of information in the buffer p, in order to occur. O is an output function that defines the set of directed arcs from T to P. O(p,t) = 1 if the arc exists, O(p,t) = 0 otherwise. An arc from a transition t to a place p indicates that when the process t is finished, it either enables the condition p, makes the resource p available, or sends an item of information to the buffer p. Figure 2-1 shows a Petri Net.

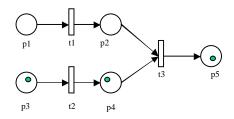

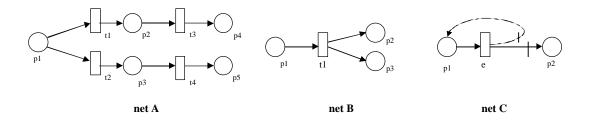

Figure 2-1 A Petri Net Example

The set of places P, the set of transitions T, and the input and output functions that define the arcs for this net are:

$$P = \{ p1, p2, p3, p4, p5 \} \qquad T = \{t1, t2, t3\}$$

$$I(p1, t1) = I(p2, t3) = I(p3, t2) = I(p4, t3) = 1, I(p, t) = 0 \text{ otherwise.}$$

$$O(p2, t1) = O(p4, t2) = O(p5, t3) = 1, O(p, t) = 0 \text{ otherwise.}$$

#### **Dynamics of Petri Net**

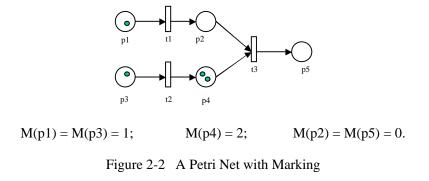

A Petri Net can contain tokens. Tokens are depicted graphically by indistinguishable dots (•), and reside in places. The existence of one or more tokens represents either the availability of the resource, or the fulfillment of the condition, or the number of items of information in the buffer. The distribution of tokens in the net is controlled by the transitions. A marking of a Petri Net is a mapping M that assigns a non-negative integer (the number of tokens) to each place. The number and position of tokens may change during the execution of a Petri Net. The tokens are used to define the execution of a Petri Net.

A transition is *enabled* by a marking if and only if all of its input places contain at least one token provided each input arc represents a single connection between the place and the transition. Formally, M(p) > 0.

An enabled transition can *fire*. The firing of the transition corresponds to the execution of the process or the algorithm. The dynamic behavior of the system is embedded in the changes of the markings. When the firing takes place, a new marking is obtained by removing a token from each input place and adding a token to each output place, M' is said to be reachable from M

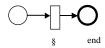

after one firing: M'(p) = M(p) + #O(p,t) - #I(p,t). As an example, consider the Petri Net in Figure 2-2 with the indicated marking.

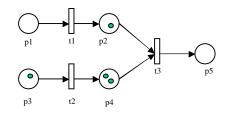

In Figure 2-2, if t1 fires, then the resulting marking is shown in Figure 2-3.

Figure 2-3 A Petri Net After Firing

Transitions t3 and t2 are now enabled. If t3 fires, the new marking is shown in Figure 2-4.

Figure 2-4 Petri Net after Second Firing

### Mathematical representation of Petri Nets -- Linear Algebraic Approach

As with any other graphs, a Petri Net with n places and m transitions can be represented by an  $n \times m$  matrix C, the *Incidence Matrix*. The rows correspond to places, the columns correspond to transitions. The cells are defined as follows:

- Cij = 1 if there is a directed arc from the j-th transition to the i-th place. "1" indicates that the firing of the j-th transition adds one token to the i-th place.

- Cij = -1 if there is a directed arc from the i-th place to the j-th transition. "-1" indicates that the firing of the j-th transition removes one token from the i-th place.

- Cij = 0 if there is no arc from the j-th transition to the i-th place.

For example, the incidence matrix of the net on Figure 2-1 is

$$C = \begin{bmatrix} t1 & t2 & t3 \\ -1 & 0 & 0^{-} & p1 \\ 1 & 0 & -1 & p2 \\ 0 & -1 & 0 & p3 \\ 0 & 1 & -1 & p4 \\ 0 & 0 & 1 & p5 \end{bmatrix}$$

#### 2.3 Software Testing

Software testing is directly concerned with software quality. The goal of testing is not to show the absence of failures in the software, but rather shows the presence of failures and gives the tester confidence on the software system. We may have different objectives for testing: to see if the software works, to find errors, or to check consistency and etc. Beizer [Bei90] defines six levels at which software testing occurs, unit test, module test, integration test, subsystem test, system test and acceptance test. Unit and module testing analyzes the local behavior of individual software blocks. Integration testing analyzes how individual block behaviors, and the interactions among blocks, contribute to the global system behavior of the system without regard to its decomposition. Subsystem testing refers to testing of coherent software subsystems before integrating into the complete system. System testing has the particular purpose to compare the software system to its original objectives, in particular validating whether the software meets the functional and non-functional requirements. Acceptance testing gets the user involved by asking if the user accepts the complete system.

Testing techniques can be categorized into two general approaches, black box and white box. Black box testing approaches create test data without using any knowledge of the structure of the software under test, whereas white box testing approaches explicitly use the program structure to develop test data. Black box testing is usually based on the requirements, specifications or design, while white box testing is usually based on the implementation in a specific programming language. White box testing approaches are typically applied during unit testing, and black box testing approaches are typically applied during integration and system testing. An important problem in software testing is deciding when to stop. Test cases are run on test programs to find failures. Unfortunately, we cannot exhaustively search the entire domain of the program (which in most cases is effectively infinite). Testing strategies may be conveniently categorized by the goal they seek to achieve. Weyuker [Wey86] has characterized these goals as adequacy criteria. Adequacy criteria are defined for testers to decide whether software has been adequately tested for a specific testing criterion [FW88]. A testing criterion is a rule or a set of rules that impose requirements on a set of test cases. Test engineers measure the extent to which a criterion is satisfied in terms of coverage, which is the percentage of test requirements that are satisfied. Test requirements are specific criteria that must be satisfied or covered, e.g., reaching statements are the requirements for statement coverage in unit testing, killing mutants are the requirements for mutation testing [DLS78], and executing definition/use pairs are the requirements in data flow testing [FW88]. There are various ways to classify adequacy criteria. One of the most common is by the source of information used to specify testing requirements and in the measurement of test adequacy. Hence, an adequacy criterion can be specification-based or program-based.

Most current testing approaches are either based on the implementation or structural information of the system or based on a requirement specification or system design, yet most high level design representations and requirement specifications are not formal enough to do this in an automated fashion. With the advent of formal architecture specification, however, architecture based test criteria can be defined based on the system properties that an ADL describes. This would support algorithmically defining test data to cover the architecture and automatically developing architectural test plans – testing at the architecture level.

#### 2.4 Issues in Software Architecture-Based Testing

As in any other testing techniques, we need to know what to test at the software architecture level and therefore we can define testing requirements at this level. Most unit level testing techniques use program structure to define test adequacy criterion, for instance, conditions (control flow) or variable define-use pairs (data flow). At the integration and system testing level, the predominant form for defining testing criteria is based on definition/use bindings [PN86], where each module *defines* or *provides* a set of facilities that are available to the *uses* or *requires* by other modules. Coupling-based testing techniques [JO98] and inter-procedural testing techniques [HR94] are such examples. These techniques use information from underlying implementation languages such as procedure calls or data sharing which means the software must already be complete. But software architecture is beyond this level [AG94c]. Software architecture focuses on the interaction between components, and normally the view of interaction is implementation-based structure information may not be possible at the software architecture level. So interaction between components will be our major focus when testing. Presentation of interaction properties of a software architecture becomes the key point.

As described in the previous section, ADLs are used to give formal definitions to software architectures. But current ADLs have different focuses on different aspects of software architecture [Med97, Cle96a]. For instance, Rapide is a general-purpose event-based description language and it allows modeling of component interfaces and their external behavior, while Wright focuses on formalizing the semantics of connections. Medvidovic and Clements [Med97, Cle96a] both give surveys on these ADLs and try to summarize what properties need

to be described in an ADL. In the proposed research, we need to extract the general properties that are important to software testing. These general properties will be useful both in testing software architectures directly as well as in software conformance testing. Once we know what we need to test, we need to define test requirements on these properties, therefore we can define general testing criteria at the software architecture level. In summary, the major issues in software architecture testing are:

- what are the general properties that are important for testing at this level?

- based on these general properties, what test requirements can be formulated?

- what general testing criteria can be defined at this level?

## 2.5 General Properties to Be Analyzed and Tested at the Architectural Level

An initial step in developing new testing methods is to enumerate the kinds of problems that can exist. We have developed some preliminary architectural testing properties. It should be emphasized that this list is tentative and work is ongoing to refine the set of properties to test for at this level. In the list of properties, a *conflict* occurs when rules, constraints or semantics cannot both be satisfied at the same time. In general, *deadlock* implies that a process does not participate in any events, but has not yet terminated successfully. A process is *deadlock free* if it can never go into a deadlock state.

1. Component Consistency Requirements: Semantics, constraints and interfaces can be associated with components. They should be consistent with respect to each other and this consistency needs to be considered at the architecture level. Interfaces have types as well as data and control constraints.

- Component constraints and semantics should have no conflicts.

- Component constraints and semantics should be deadlock free.

- Component constraints and semantics should have no conflicts with the component interface constraints.

- Connector Consistency Requirements: A connector also contains interfaces, semantics, and constraints that need to be consistent. Interfaces have types as well as data and control constraints.

- Connector constraints and semantics should have no conflicts.

- Connector constraints and semantics should be deadlock free.

- Connector constraints and semantics should have no conflicts with the associated connector interfaces constraints.

- 3. Component-Connector Compatibility Requirements: Component interfaces are associated with connector interfaces to enable interactions. Informally, *compatibility* means that a component interface behaves in a manner that is consistent with assumptions made by the connector.

- Component interfaces should be compatible with the associated connector interfaces.

- For some compatibility requirements, it must be determined whether the component/connector relationship is deadlock free.

- 4. Configuration Requirements: The configuration of a software architecture should be tested against several test requirements. An *initiation state* is the "start state", the state that the

system is initially in. There are explicit *data flows* through the architecture of the system; a data element is given a value (*defined*) in its *source component* and the value is used in a *target component*. There are also explicit *control flows*; each architecture element has one or more designated *next element*. This transfer of execution could be between states in a component, through connectors, or across components.

- Data Flow Reachability: A data element should be able to reach its designated target component from its source component through the connectors. The data element should reach the target component without having its value modified.

- Control Flow Reachability: Every architecture element should be able to reach its designated next element.

- Connectivity: A component or connector interface with either no next element or no

previous element is said to be "dangling". Dangling components and connector

interfaces could indicate potential problems.

- Interactions that in isolation are deadlock free can interact in such a way as to cause a deadlock situation. It should be the case that the system is deadlock free.

- 5. Style Restriction Requirement: The architecture style being used imposes some constraints on the software configuration. The system being used must satisfy those constraints.

System-level tests derived from architectures can validate that the software implements the architecture correctly and help to verify the architecture. If the architecture is sufficiently descriptive, then the tests should be effective at finding problems in the implementation. In this dissertation, we only discuss test case generation technique, analysis and evaluation of the ADL specification is not in the scope of this research.

#### 2.6 Related Work

Related work for this research covers the following areas: ADL survey, formal definition of software architecture, architecture-based dependency analysis and testing, component adequacy testing and mismatches of components.

#### 2.6.1 ADL Classification and Survey

Medvidovic [Med97] gives a survey of most of the current ADLs and summarizes some software architecture properties that current ADLs can describe. This survey classifies and compares properties in components, connections, and configurations and how they are represented in these ADLs. It makes an attempt to answer the question of what an ADL is and why, and how it compares to other ADLs. Such information is very important for understanding current status of ADLs. Even though the architectural properties these ADLs describe are not specific for testing purpose, they help us understand and pick the properties to test.

## 2.6.2 Formal definition of Software Architecture

Allen [All97] shows that an Architecture Description Language based on a formal, abstract model of system behavior can provide a practical way to describe and analyze software architectures and architectural styles. He introduces Wright, an architectural description language based on the formal description of the abstract behavior of architectural components and connectors. Wright uses explicit, independent connector types as interaction patterns, it describes the abstract behavior of components using a CSP-like notation, and styles can be characterizes by using predicates over system instances. His work also shows some static checks to determine the consistency and completeness of an architectural specification.

#### 2.6.3 Correctness and Composition of Software Architectures

Moriconi and Qian [MORI94] discuss correctness and composition of software architectures. In their paper, they provide a formal criterion for proving that one architecture implements another architecture, even if they are described in different architectural styles. They use first-order logic for the definition of both configuration and style structures, and provide a specific model of style-based refinement of configurations.

## 2.6.4 Architecture-level Dependency Analysis & Testing

Richardson and Wolf present their research in architecture-based dependency analysis and testing [RW96, SRW97, SRW98]. The Chemical Abstract Machine (CHAM) model is used to represent software architectures. The CHAM for a software architecture defines molecules (elements), solutions (combinations of elements), and transformation rules that specify how solutions evolve. Dependency analysis is based on structural relationships (textual inclusion, import/export, inheritance) and behavioral relationships (temporal, state-based, causal, input/output). The structural dependencies allow one to locate source specifications that contribute to the description of some state or interaction. The behavioral dependencies allow one to relate states or interactions to other states or interactions. These relations are recorded in a table for dependency analysis. Testing criteria are defined based on the CHAM model. For example, all-data-elements requires that all data defined in the architecture are communicated (for each data element d, at least one solution contains a molecule involving d), and allprocessing-elements requires that all processing elements are executed (for each processing element p, at least on solution contains a molecule involving p). However it has been argued [All97] that CHAM describes the structure and abstract behavior of a single configuration, rather than a class of systems. Medvidovic [Med97] also argues that even though CHAM can be used effectively to prove certain properties of architectures, the interface topology is implicit in the solution and transformation rules. So this does not meet the requirements to be an ADL.

#### 2.6.5 Component-based Testing

Rosebblum [Rosen00, Rosen97] initiates the development of a component-based software testing theory. Two concepts were defined: the concept of C-adequate-for-P for adequate unit testing of a component and the concept C-adequate-on-M for adequate integration testing of a component-based system. This technique views testing of component-based software as both a unit testing problem for program M, and an integration testing problem for program P containing M. The unit-testing viewpoint requires the developer of M to test M with criterion C and to carry out the testing with a test set that is C-adequate-for-P. The integration testing viewpoint requires the developer of P to test P with a test set that is C-adequate-on-M. If the test adequacy criteria being used are code coverage criteria, then satisfaction of these requirements can be checked. A formal model of component-based software was defined, and the model was used to formally define a notion of test adequacy for component-based systems. The notion of component as used in this technique corresponds to a general object-oriented notion of a component. A component M encapsulates some state and provides a well-defined interface that strictly governs access to the state by other parts of a system containing the component. The interface is viewed as a set of methods or operations that can be applied to the component. Generally speaking, this technique is at the integration level rather than at the architectural level and it is also based on the completeness of the implementation. This work is different from the testing technique proposed in this dissertation.

## Chapter 3 Software Architecture-based Testing Technique

Traditionally, software system level testing has been based on informal, manual, and ad-hoc analyses of the system requirements. This informality may make it hard to distinguish different levels of abstraction throughout the process and thus may lead to inconsistent testing results and lack of repeatability in the process. Formalized software architecture description languages represent significant opportunities for testing because they formally describe how the software system is expected to behave in a high level view that allows test engineers to focus on the overall system structure, and also in a form that can be handled automatically.

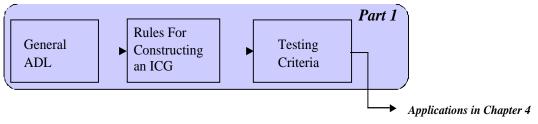

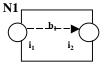

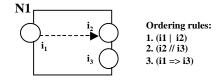

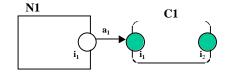

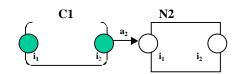

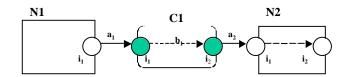

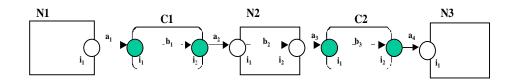

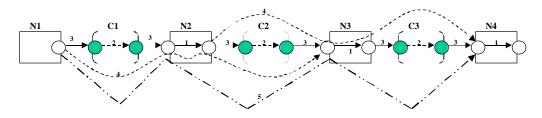

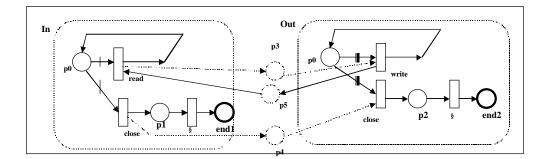

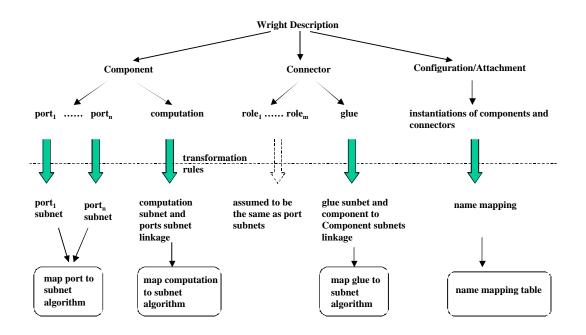

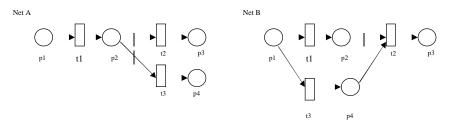

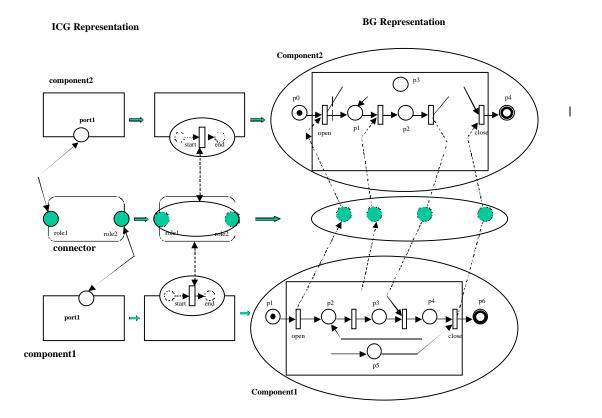

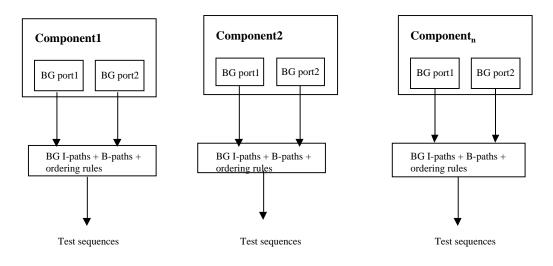

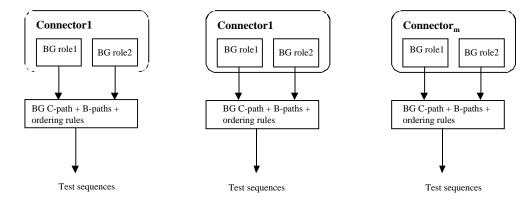

This chapter discusses a new software testing technique at the software architecture level. As we have discussed in Chapter 1, the overall topology is presented in three parts: Testing Techniques for General ADLs, Applying the Technique to a Specific ADL, and Tests for an Implementation. This chapter focuses on presenting a testing technique for general ADLs, shown in Figure 3-1. We introduce a graphical representation Interface Connectivity Graph (ICG) and the construction of an ICG, then define the testing requirements and testing criteria defined based on the ICG. The testing criteria may serve as guidelines for testers to decide when to stop testing. Test coverage measurement is also discussed at the end of this chapter.

We use the following definitions here and after this chapter. *Test requirements* are specific things that must be satisfied. For example, *reaching statements* are the requirements for statement coverage, and *killing mutants* are the requirements for mutation testing. A *testing*

*criterion* is a rule or a collection of rules that imposes requirements on a set of test cases. Testers ensure the extent to which a criterion is satisfied in terms of *coverage*, which is the percentage of requirements that are satisfied.

## Testing Technique for General ADLs

Figure 3-1 Testing Technique Procedures

## 3.1 Basic Definitions

To make architecture-based testing a manageable process, testing must be guided by the definition of the architecture. As we have discussed, software architecture must be specified using its own specification languages and analysis techniques in order to achieve benefits. A large number of ADLs have been proposed, each of which specifies a particular approach and specifies certain aspects of a software architecture. Even though there is no unique definition of what an ADL should describe, we need to understand what software architecture aspects an ADL should describe and start testing those aspects.

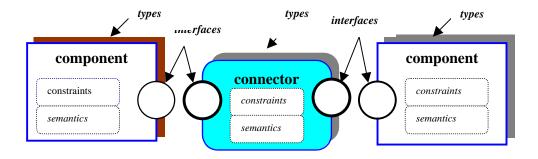

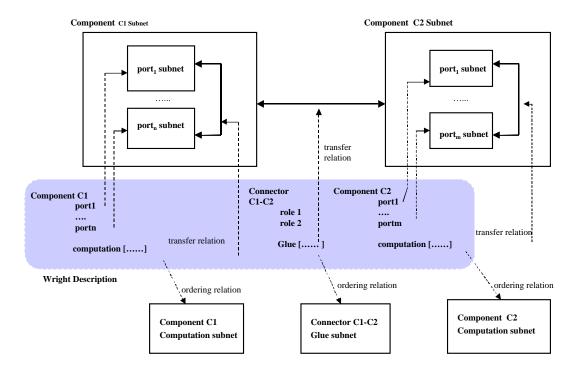

Before we discuss the general architectural aspects that need to be tested, we first define some terms taken from Medvidovic's paper [Med97]. We view software architecture as components, connectors and configuration. For each component and connector, its interface, types, constraints and semantics are defined.

A Component's Interface is a set of interaction points between this component and other components that this component interacts with. It specifies the services (messages, operations, and variables) a component provides. Interfaces in ADLs are represented as either ports (as in Wright) or *constituents* (as in Rapide). ADLs support reuse by modeling abstract components as types and instantiating them multiple times in an architectural specification. Abstract component types can also be parameterized to further facilitate reuse. *Component Semantics* is a description of component behavior; it enables analysis, constraint enforcement, and mappings of architectures across levels of abstraction. Component Constraints is a property of or assertion about a system or one of its parts. Constraints are specified to ensure adherence to intended component uses, enforce usage boundaries, and establish intra-component dependencies. A connector's interface is a set of interaction points between it and the components attached to it. It enables proper connectivity of components and their communication in a software architecture. Architecture-level communication is often expressed with complex protocols. To abstract away these protocols and make them reusable, ADLs should model connectors as Connector Types. Connector Semantics provides connector protocol and transaction semantics so as to be able to perform analyses of component interactions, consistent refinements across levels of abstraction, and enforcement of interconnection and communication constraints. Not every ADL models connector semantics. Connector Constraints specifies constraints to ensure adherence to interaction protocols, establish intra-connector dependencies, and enforce usage boundaries. In order to describe software systems at different levels of detail, architecture configurations *Compositionability* supports the situations where a software architecture may

become a mere component in a bigger architecture or vise versa. Architecture *Configurations Constraints* describe desired dependencies among components and connectors in a configuration.

Figure 3-2 shows these aspects in a software architecture. These architecture aspects will be used for the software architecture-based testing. From now on, we name components, connectors, interfaces of components and connectors as the *architecture units*. Other architecture aspects such as constraints and semantics will be used to define possible relationships among these architecture units. Configuration will be considered as the instantiation of the architecture units. When it comes to a specific ADL description, it may not have all these aspects defined explicitly or defined at all. For instance, Rapide [LV95] does not explicitly describe a connector, it has no constraints or semantics for the connector. So when applying architecture-based testing technique to a specific ADL, we will only consider those aspects that are described in the ADL, therefore, the application of this testing technique will vary based on the ADL used.

Figure 3-2 Architecture Aspects

## 3.2 Architecture-based Testing Technique for General ADLs

Relations among architecture units are the key factors in a software architecture description, they define the behaviors and connectivities among software components via connectors. Our software architecture-based testing technique focuses on testing the relations among architecture components. Therefore, we define relations among architecture units as software *architecture relations*. The technique requires that tests cover certain architecture relations among components and connectors or inside a component and a connector. These architecture relations are based on the possible bindings: data transfer, control transfer, and execution ordering rules. Formal descriptions of these relations are defined in the next section. The underlying premise of the architecture components and connectors, it must be ensured that all the existing architecture relations be covered in the test. Because this technique is limited to the architecture description, it is only concerned with relations at the architecture level, not with detail design or implementation level, but they can be extended to the software design or implementation level.

## 3.2.1 What Needs to be Tested at the Architecture Level – Testing Requirements

Given architecture relations among components, interfaces, and connectors, software architecture testing needs to focus on testing the following aspects:

- 1. *Testing component to connector connectivity*: this tests the connectivity and compatibility from a component interface to a connector interface.

- 2. *Testing connector to component connectivity*: this tests the connectivity and compatibility from a connector interface to a component interface.

- 3. *Testing component internal interfaces*: this tests the possible data transfer, control transfer, and ordering relations among the interfaces inside a component.

- 4. *Testing connector internal interfaces:* this tests the possible data transfer, control transfer, and ordering relations among the interfaces inside a connector.

- Testing direct component to component connectivity: this tests the connection of two components through a connector.

- 6. *Testing indirect component to component connectivity*: this tests a subset of components and connectors that are indirectly data or control related.

- 7. *Testing whole structure connectivity*: this tests the overall architecture structure connectivity. All connections among components, connectors and all internal connections are tested.

#### 3.2.2 Architecture-based Testing Concepts

Testing at the unit level focuses on relations on program units, such as statements, variables, or conditions. Testing at the architecture level should focus on the *architecture relations* of the architecture units specified by a specific ADL description. This section defines some concepts for the architecture relations. To visualize the architecture relations, a graphical representation of the architecture is introduced in this section, we then can derive testing requirements and testing criteria based on this graphical representation.

## 3.2.2.1 The Interface Connectivity Graph (ICG)

Testing adequacy criteria help to tell testers when testing is enough and when to stop. Graphical representations have long been used to help to visualize the definition of testing criteria. For instance, data flow diagrams, control flow diagrams, state transition diagrams, etc., have all been used in defining testing criteria and in generating testing cases. Therefore, we introduce graphical representations to help visualize our architecture-based testing technique. The Interface Connectivity Graph (ICG) represents the connectivity relationships between components and connectors as well as relations inside a component and a connector.

An ICG is composed of a set of components (visually as rectangular boxes), component interfaces (clear circles on the edge of the component boxes), connectors (round boxes), connector interfaces (shaded circles on the edge of the connector boxes), connections between connectors and components (solid arrows), and connections inside components or connectors (dash-line arrows).

Definition 3.1 Architecture Interface Connectivity Graph (ICG)

Given a software architecture defined by a specific ADL, the architecture Interface Connectivity Graph (ICG) is defined as:

ICG = (N, C, N\_Interf, C\_Interf, N\_Ex\_arc, C\_Ex\_arc, N\_In\_arc, C\_In\_arc),

- $N = \{N_1, N_2, \dots, N_n\}$ , a finite set of components

- $C = \{C_1, C_2, \dots, C_m\}$ , a finite set of connectors

- N\_Interf = {N<sub>1</sub>.interf<sub>1</sub>, ... N<sub>1</sub>.interf<sub>s</sub>, ... N<sub>n</sub>.interf<sub>1</sub>, ... N<sub>n</sub>.interf<sub>x</sub>}, a finite set of component interfaces

- $C_{Interf} = \{C_{1}.interf_{1}, ..., C_{m}.interf_{t}\}, a finite set of connector interfaces$

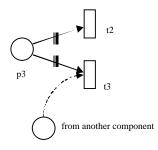

- N\_Ex\_arc is defined as (N × C) {0, 1}, if N\_Ex\_arc(n, c) = 1, then the arc exists, there is a connection between the component interface to a connector interface, otherwise the arc does not exist

- C\_Ex\_arc is defined as (C × N) {0, 1}, if C\_Ex\_arc(n, c) = 1, then there is an arc between a connector to a component interface, otherwise the arc does not exist

Because C\_Ex\_arc and N\_Ex\_arc contain arcs that connect components and connectors, they are viewed as the external arcs. Internal arcs represent the connections between interfaces of one component or they represent the connections between interfaces of one connector. Internal arcs are defined as follows.

- N\_Inter\_arc = (C\_Interf × N\_Interf) {0, 1}, if N\_In\_arc (n.interf<sub>1</sub>, n.interf<sub>2</sub>) = 1, then there is a connection between n.interf<sub>1</sub> and n.interf<sub>2</sub>, otherwise there is no such an arc

- C\_Inter\_arc = (C\_Interf × C\_Interf) {0, 1}. If C\_Inter\_arc (c.interf<sub>1</sub>, c.interf<sub>2</sub>) = 1, then there is an arc c.interf<sub>1</sub> and c.interf<sub>2</sub>. Otherwise, there is no such an arc